IC 74LS145 là bộ giải mã BCD sang Decimal dựa trên TTL được sử dụng để điều khiển mười đầu ra nhị phân trên cơ sở bốn đầu vào nhị phân. IC bao gồm tám biến tần và mười cổng NAND có bốn đầu vào.

Tổng số mười tám cổng này đi kèm với một mạch thông minh cung cấp mười đầu ra thông qua các cổng NAND. Các đầu vào đi qua bốn cổng NAND. Bốn đầu vào có giá trị nhỏ nhất bằng 0000 và giá trị lớn nhất bằng 1111.

IC đảm bảo rằng nó cho đầu ra CAO trên các đầu vào không hợp lệ và nó cũng cho đầu ra THẤP trên một đầu ra duy nhất trên các đầu vào cụ thể. IC tương thích để sử dụng với bất kỳ mạch tích hợp TTL, DTL hoặc và MOS nào.

IC được thiết kế để sử dụng như các mạch logic bộ thu mở và sử dụng làm chỉ báo / trình điều khiển cho rơ le. Nó có mức tiêu tán Công suất thấp và trong các điốt kẹp IC điều khiển sự kết thúc ở tốc độ cao.

Các tương đương khác của IC này là SN74LS145, SN54145, SN54LS145, SN74145.

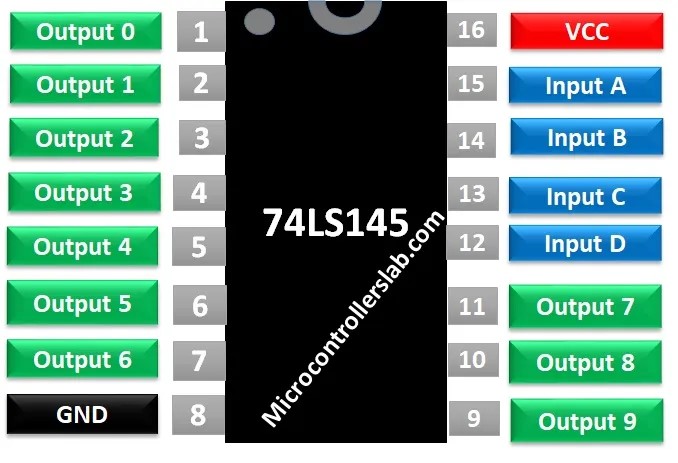

Sơ đồ chân của DCB tới bộ giải mã thập phân được hiển thị ở đây. Các mẫu màu khác nhau được sử dụng để phân biệt các chân đầu vào, đầu ra và chân cấp nguồn.

| PINS | Chi Tiết | |

| Q0 | Pin 1 | Chân 1 đến Chân 7 sẽ được sử dụng làm 7 chân đầu ra đầu tiên trên 7 đầu vào đầu tiên. Các chân này sẽ ở trạng thái CAO khi không có đầu vào hoặc đầu vào không hợp lệ trên các chân đầu vào. Trong trường hợp đầu vào ảnh hưởng đến đầu ra, chân sẽ thay đổi trạng thái từ THẤP đến CAO cho đến khi đầu vào thay đổi thành đầu vào mới hoặc không hợp lệ. Chỉ một chân đầu ra sẽ THẤP tại đầu vào cụ thể. |

| Q1 | Pin 2 | |

| Q2 | Pin 3 | |

| Q3 | Pin 4 | |

| Q4 | Pin 5 | |

| Q5 | Pin 6 | |

| Q6 | Pin 7 | |

| GND | Pin 8 | Pin 8 sẽ được sử dụng làm điểm chung. Nối đất của Bộ nguồn và các thiết bị tương thích khác sẽ được nối chung với Chân 8 để có thể sử dụng được với IC. |

| Q7 | Pin 9 | Chân 9 đến Chân 11 cũng sẽ được sử dụng làm chân đầu ra. Trong các chân này, đầu ra cũng sẽ hoạt động giống như bảy chân đầu tiên. Chỉ một chân (từ bảy chân đầu tiên và ba chân này) sẽ bị ảnh hưởng bởi các đầu vào tại một thời điểm. |

| Q8 | Pin 10 | |

| Q9 | Pin 11 | |

| P0 | Pin 12 | Chân 12 sẽ được sử dụng làm chân đầu vào đầu tiên cho IC 74LS145. |

| P1 | Pin 13 | Pin 13 sẽ được sử dụng như một chân đầu vào thứ hai cho IC 74LS145. |

| P2 | Pin 14 | Chân 14 sẽ được sử dụng làm chân đầu vào thứ ba cho IC 74LS145. |

| P3 | Pin 15 | Chân 15 sẽ được sử dụng làm chân đầu vào thứ tư cho IC 74LS145. |

| VCC | Pin 16 | Chân 15 sẽ được sử dụng làm chân đầu vào thứ tư cho IC 74LS145. |

Thông tin thêm về thông số kỹ thuật và tính năng có sẵn trong biểu dữ liệu của 74LS145.

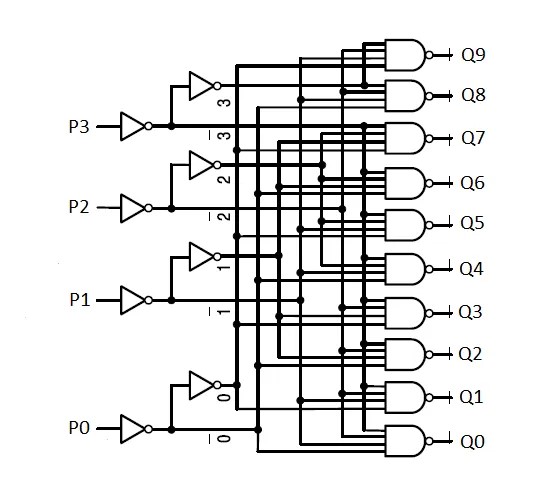

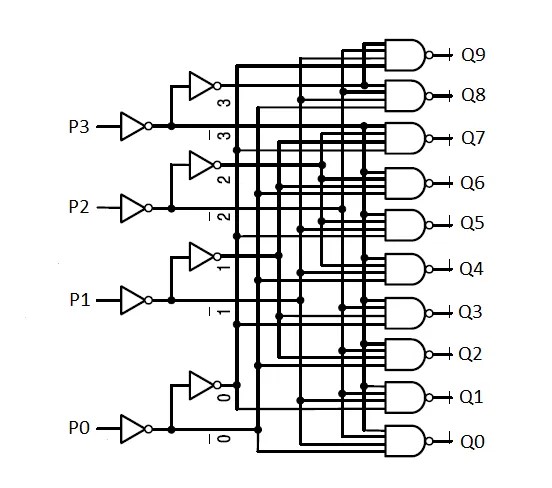

Trong IC 74LS145 mạch gồm 8 cổng NOT và 10 cổng NAND. Hai cổng NOT được kết nối với mỗi đầu vào và một cổng NAND duy nhất được kết nối với mỗi đầu ra. Mỗi cổng NAND nhận bốn đầu vào và mọi đầu ra đều được đảo ngược từ cổng NAND. Sẽ có tổng cộng 11 điều kiện mà mạch sẽ hoạt động và chúng ta cần hiểu mỗi đầu vào sẽ cho đầu ra cụ thể như thế nào.

Trong IC 74LS145 chúng ta có tổng cộng 16 đầu vào nhưng chỉ từ 0000 đến 1001 sẽ có thể làm cho đầu ra THẤP còn lại sẽ không ảnh hưởng đến OUTPUT, điều này làm cho trạng thái từ 0101 đến 1111 là trạng thái không hợp lệ.

IC sẽ luôn tuân theo bảng sự thật sau đây. Mọi điều kiện đầu vào sẽ làm cho đầu ra THẤP và những người không thể thay đổi trạng thái đầu ra sẽ được gọi là trạng thái không hợp lệ. Trạng thái không hợp lệ sẽ không thể thay đổi dù chỉ một cổng NAND từ CAO thành THẤP do Mạch. 10 trạng thái duy nhất sẽ có thể thay đổi các đầu ra làm cho mạch giải mã 1-10 quá.

| INPUTS | OUTPUTS | ||||||||||||

| P3 | P2 | P1 | P0 | Q0 | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Q7 | Q8 | Q9 |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

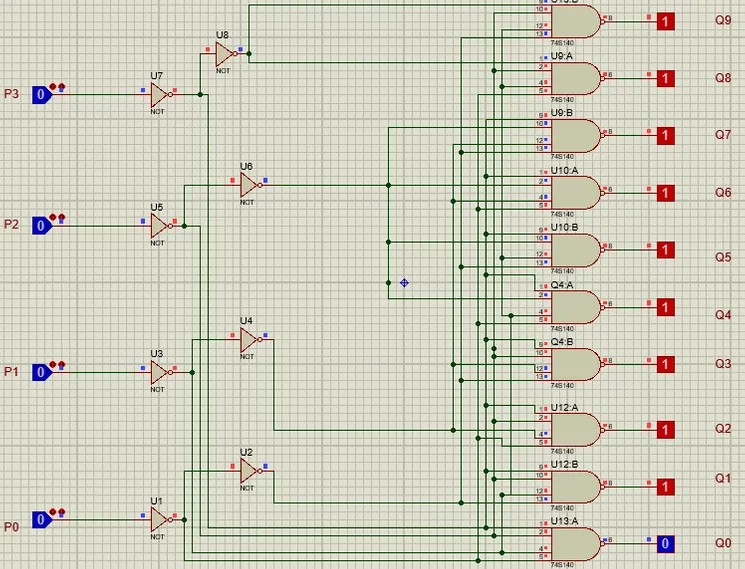

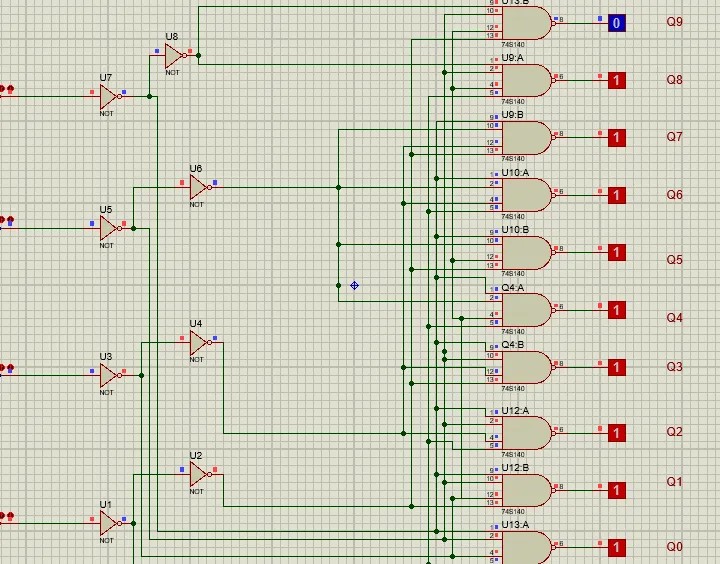

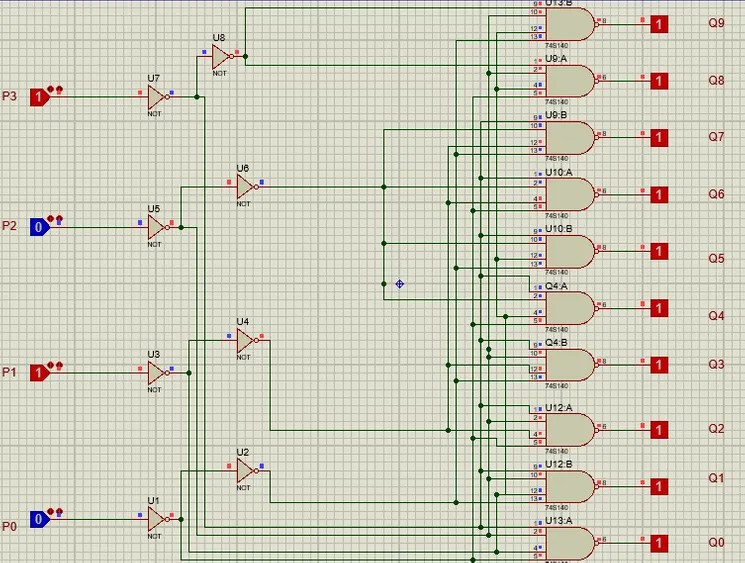

Trong ví dụ này, chúng ta sẽ hiểu chức năng của vi mạch trên ba trạng thái “0000” là trạng thái đầu tiên, trạng thái cuối cùng 1001 và trạng thái không hợp lệ. Đầu tiên thiết kế mạch IC trong Proteus. Sử dụng các cổng logic để hiểu chức năng của vi mạch. Thiết kế mạch theo sơ đồ sau:

Đầu tiên, nhập đầu vào là “0000”. Bạn sẽ nhận thấy rằng đầu vào sẽ chỉ làm cho Q0 hoạt động, điều này sẽ làm cho đầu ra THẤP và các đầu ra khác sẽ vẫn ở mức CAO.

Trong một trường hợp khác khi đầu vào là 1001 thì Q9 sẽ là THẤP và các đầu vào khác sẽ vẫn CAO.

Trong trường hợp các giá trị từ giá trị từ 0000 đến 1001, logic sẽ đi theo các đường dẫn khác nhau để làm cho các cổng khác hoạt động nhưng trong trường hợp các giá trị trên 1001, sẽ không có bất kỳ đường dẫn nào và kết quả đầu ra sẽ vẫn CAO cho tất cả các cổng.

Các trạng thái logic sẽ không hoạt động bất kỳ cổng nào. Đó là lý do tại sao những trạng thái này được gọi là trạng thái Không hợp lệ. IC có nhiều mục đích sử dụng do tốc độ nhanh và sử dụng với bộ điều khiển khác.

Bất cứ khi nào chúng ta cần sử dụng bộ điều khiển, chúng ta sẽ chỉ cần sử dụng các đầu vào hợp lệ, nếu không IC sẽ không đưa ra bất kỳ đầu ra nào, tất cả sẽ vẫn ở mức CAO cho đến khi có đầu vào hợp lệ.

>>> 100+ Mã Sản Phẩm Dây Rút: https://mecsu.vn/san-pham/day-rut-nhua.5op

>>> 1000+ Mã Sản Phẩm Đầu Cosse: https://mecsu.vn/san-pham/dau-cosse.Q1j

>> Mời anh em xem thêm