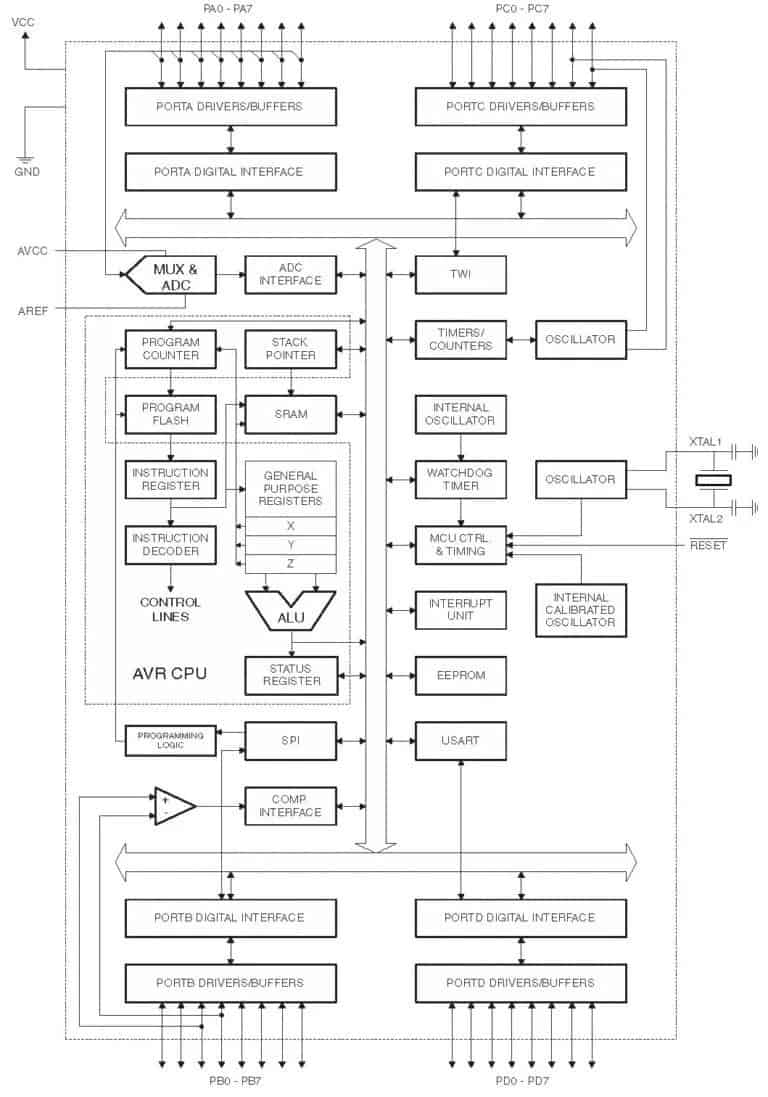

ATMega16 là một trong những bộ vi điều khiển rẻ nhất và được sử dụng nhiều nhất do có nhiều chân và chức năng. Nó gần giống với ATmega328P nhất nhưng có dung lượng bộ nhớ nhỏ hơn và số chân cắm lớn hơn.

ATMEL đã thiết kế ATMega16 bằng cách sử dụng thiết kế CPU RSIC và công nghệ CMOS 8-bit giúp tương thích với các thiết bị TTL / CMOS khác với hoạt động tiêu thụ ít điện năng.

Cấu trúc bên trong cho phép nhà thiết kế sử dụng chế độ ngủ, tối ưu công suất và hiệu suất. Bộ vi điều khiển có package tow và có các chân khác nhau ở các package khác nhau.

AVR ATmega16 là vi điều khiển CMOS 8-bit công suất thấp dựa trên kiến trúc vi mạng RISC nâng cao của AVR. Thông lượng AVR ATmega16 khoảng 1 MIPS trên mỗi MHz sử dụng một xung clock duy nhất cho mỗi lệnh cho phép nhà thiết kế tối ưu hóa mức tiêu thụ điện năng với tốc độ xử lý.

AVR có 32 thanh ghi chức năng chung và một tập lệnh phong phú. Chúng được kết nối trực tiếp với bộ ALU và cho phép truy cập hai thanh ghi độc lập trên cùng một lệnh duy nhất được thực thi trong một chu kỳ xung clock.

Tham khảo các hướng dẫn vi điều khiển Avr giúp bạn hiểu các ví dụ real-time. Phần mềm Atmel Studio 6 được sử dụng để viết code c và tạo tệp hex.

Nguồn cấp: Mọi vi điều khiển đều cần nguồn điện để hoạt động và ATMega16 có ba chân cấp nguồn, một là đầu vào cấp nguồn và hai chân còn lại là chân ground và được kết nối bên trong với nhau. Các chân đó trong bộ vi điều khiển là:

Bộ tạo dao động: ATMega16 có bộ dao động 8MHz bên trong (có thể thay đổi tần số) nhưng để mở rộng tốc độ xung clock, bộ dao động bên ngoài sẽ sử dụng các chân dao động dưới đây:

I/O digital: Trong ATMega16 có bốn cổng (A, B, C & D) với tổng số 32 chân đầu vào / đầu ra. Tất cả các chân này có thể được sử dụng cho bất kỳ chức năng điều khiển I/O nào với các thiết bị ngoại vi. Các chân đó trong ATMega16 được đưa ra dưới đây:

Interrupt: Đây là một trong những chức năng được sử dụng nhiều nhất để thay đổi điện áp cao nhưng chức năng cơ bản là tạo sự kiện xử lý cho CPU. Trong bộ vi điều khiển này, có tổng cộng ba bộ ngắt có thể được sử dụng với các module bên ngoài hoặc cấp tín hiệu từ một nút nhấn để tạo tín hiệu cho phép xử lý sự kiện nào đó trên CPU. Các chân này trong ATmega16 được liệt kê bên dưới:

USART: Các chân UART trong vi điều khiển thực hiện giao tiếp với các thiết bị nối tiếp. Nó sử dụng hai chân giao tiếp và một số lệnh lập trình bên trong để giao tiếp nhưng những chân này cũng có thể được sử dụng để lập trình bằng cách sử dụng chân thứ ba được gọi là chân xung clock. Các chân xung clock cũng có thể được sử dụng để giao tiếp dữ liệu đơn giản thay vì phải lập trình. Tất cả các chân đó trong bộ vi điều khiển được liệt kê bên dưới:

SPI: Giao thức SPI là một trong những giao thức truyền thông nối tiếp tốt nhất cho nhiều module. Nó có thể được sử dụng trong trường hợp có nhiều thiết bị ngoại vi giao tiếp với bộ vi điều khiển. Các 4 dây giao tiếp, hai dây cho dữ liệu và một dây cho xung clock, và một dây chọn thiết bị giao tiếp. Chân lựa chọn thiết bị được biết đến là chân Select Slave và được xác định trước trên bộ vi điều khiển nhưng các chân đầu ra cũng có thể thực hiện chức năng của chân SS bằng cách lập trình. Giao thức SPI không chỉ sử dụng để giao tiếp mà nó còn có thể được sử dụng để lập trình vi điều khiển. Tất cả các chân SPI của ATMega16 là:

I 2 C: Một số cảm biến và động cơ servo có giao thức truyền thông nối tiếp I 2 C. Để giao tiếp với các thiết bị ngoại vi đó, ATMega16 cũng hỗ trợ giao thức I2C. Một chân được sử dụng để giao tiếp dữ liệu và một chân là xung clock. Cả hai chân được liệt kê dưới đây:

JTAG: Các chân này có trong hầu hết các bo mạch cho mục đích test. Lý do thiết kế JTAG là để kiểm tra thiết bị và mạch PCB sau khi nhà sản xuất hoàn thành thiết kế. JTAG được kết nối với cổng test bên trong nhưng cũng có thể được sử dụng để lập trình bộ vi điều khiển và thậm chí cả bộ bootloader. Các chân JTAG trong vi điều khiển là:

Timer: Bộ vi điều khiển có ba bộ định thời / bộ đếm bên trong. Chúng có thể hoạt động bằng cách sử dụng bộ dao động bên trong hoặc bộ dao động của vi điều khiển, nhưng cũng có thể thực hiện đếm bằng cách sử dụng bộ dao động bên ngoài riêng. Hai bộ định thời 8-bit và một bộ định thời 16bit, chỉ có hai bộ định thời hỗ trợ các chân đầu vào xung clock bên ngoài. Tất cả các bộ định thời và chân dao động cho bộ định thời được đưa ra dưới đây:

Bộ so sánh analog: bộ so sánh trong vi điều khiển dùng để so sánh tín hiệu analog. Bộ so sánh lấy hai đầu vào đảo và không đảo của cùng một tín hiệu. Sau khi so sánh tín hiệu analog bên trong, tín hiệu đầu ra được sử dụng bên trong hoặc thực hiện các chức năng khác nhưng tất cả chúng sẽ được xử lý bằng lập trình. Các chân so sánh analog trong ATMega16 được liệt kê dưới đây:

Capture / Compare / PWM: PWM là chức năng cơ bản cho hầu hết các thiết bị để điều chỉnh điện áp. Trong ATMega16 có bốn chân PWM sử dụng Prescaler để tạo ra tín hiệu đầu ra mong muốn. Các chân đó là:

Đầu vào capture: ATMega16 có thể tính toán chu kỳ và tần số xử lý của xung bên ngoài. Kết quả tính toán được sử dụng để thực hiện các hoạt động tiếp theo. Chỉ có một chân trong bộ vi điều khiển có thể làm điều đó, được liệt kê bên dưới:

Bộ chuyển đổi tín hiệu analog sang digital: ADC có trong mọi vi điều khiển do đầu ra của nhiều module có dạng tín hiệu analog và ATMega16 hỗ trợ 8 kênh A / D. Trong bộ vi điều khiển, tất cả ADC có thể chuyển đổi analog riêng lẻ nhưng bộ chuyển đổi analog đầu tiên sẽ yêu cầu nguồn điện bên ngoài để hoạt động ở các chân AVCC của nó. Tất cả các chân này được đưa ra bên dưới:

AREF: Giá trị tối đa của tín hiệu analog được xác định bởi điện áp cấp, đôi khi tác động không mong muốn đến đầu ra do các mức điện áp khác nhau của thiết bị có đầu ra analog. Để khắc phục vấn đề này, một chân tham chiếu analog được sử dụng, điện áp của thiết bị đầu ra analog sẽ được sử dụng để so sánh đầu ra theo các mức điện áp ở chân này. Chân Aref trong bộ vi điều khiển được liệt kê bên dưới:

RESET: Để thiết lập lại vi điều khiển ATMega16, một chân reset nội bộ và bên ngoài được sử dụng. Reset bên trong được sử dụng thông qua lập trình nhưng để sử dụng reset bên ngoài, cần một tín hiệu xung logic thấp để kích hoạt vào chân dưới đây:

| TÍNH NĂNG & THÔNG SỐ KỸ THUẬT | |

| Kiến trúc CPU | RISC 8-bit |

| Tần số CPU | 16MHz |

| Dải điện áp hoạt động | (4,5V - 5,5V) |

| Cổng GPIO | 32 chân I / O |

| Bộ Ngắt | 3 |

| Timer | 3 (Hai timer 8 bit và một timer 16 bit) |

| PWM | 4 CCP |

| ICP | 1 chân ICP |

| USART | Một kênh USART |

| Giao thức nối tiếp | Một giao diện nối tiếp (hai dây) |

| I2C | Một kênh I2C |

| SPI | Một kênh SPI |

| JTAG | Có |

| Self-Programming | Có |

| Timer watchdog | Có |

| LAN | Không có |

| CAN | Không có |

| ADC | 8 kênh |

| Module USART nâng cao | 1 kênh |

| SRAM | 1Kb |

| FLASH (Bộ nhớ chương trình) | 16Kb |

| EEPROM | 512 byte |

| Bộ so sánh | 1 |

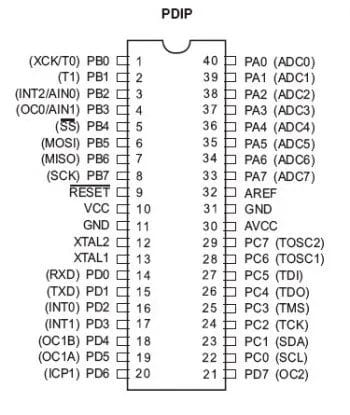

| Các package | PDIP (40 chân), TQFP (44 chân) & MLF (44 chân) |

Cổng A (PA7-PA0) được sử dụng làm đầu vào analog của A / D. Nhưng nếu bộ chuyển đổi A / D không được kích hoạt, nó cũng có thể làm I/O dữ liệu hai chiều 8 bit. Các chân cổng này có điện trở kéo bên trong (được chọn cho mỗi bit).

Cổng B (PB7-PB0) được sử dụng làm cổng I/O hai chiều 8 bit có điện trở kéo bên trong. Các bộ đệm đầu ra của cổng B có đặc tính điều khiển đối xứng với dòng sink và source cao.

Cổng C (PC7-PC0) Điểm đặc biệt của cổng C là có giao thức JTAG. Nếu giao thức JTAG được bật, các điện trở kéo ở các chân PC5 (TDI), PC3 (TMS) và PC2 (TCK) sẽ được kích hoạt ngay cả khi thức hiện reset. Cũng có thể được sử dụng làm cổng I/O hai chiều 8 bit có điện trở kéo bên trong.

Cổng D (PD7-PD0) Cổng D có các tính năng đặc biệt khác nhau của vi điều khiển ATmega16 như đầu vào ngắt, đầu ra bộ định thời / bộ đếm và UART. Ngoài ra, Cổng D còn được sử dụng làm cổng I/O hai chiều 8 bit có điện trở kéo bên trong.

ATmega16 có thể lựa chọn các nguồn xung nhịp bằng các bit Flash Fuse như hình bên dưới.

Nguồn cấp xung clock đã chọn được đưa vào bộ tạo xung nhịp AVR và được chuyển đến các module thích hợp.Các bit 1111 hoặc 1010 để chọn nguồn xung clock cấp từ sự kết hợp của bộ dao động thạch anh bên ngoài hoặc bộ cộng hưởng.

Với thạch anh tần số thấp bên ngoài là 1001 và với bộ tạo dao động RC bên ngoài là 1000 hoặc 0101. Bộ dao động RC bên trong đã hiệu chỉnh là 0100 hoặc 0001 và với xung clock bên ngoài là 0000 . Bit “1” có nghĩa là chưa được lập trình và “0” là đã được lập trình.

Giao tiếp UASART nối tiếp giữa bộ điều khiển và modem GSM. Bộ thu và phát tín hiệu nối tiếp đồng bộ và không đồng bộ (USART) là module giao tiếp nối tiếp rất mượt. Tốc độ Baud chung được hỗ trợ là 1200, 1800, 2400, 4800, 7200, 9600, 14400, 19200, 38400, 57600, 115200. Phần cứng USART nối tiếp bao gồm:

Thanh ghi tốc độ Baud của USART có hai thanh ghi UBRRH và UBRRL, có tổng cộng 16 bit. Thanh ghi UBRRH có cùng một vị trí I / O với Thanh ghi UCSRC. Bit 15 (URSEL) này lựa chọn giữa việc truy cập thanh ghi UBRRH hoặc thanh ghi UCSRC.

Bit này có logic 0 khi đang đọc và ghi thanh ghi UBRRH. Bit 14:12 là các bit dự phòng (reserved) để sử dụng cho mục đích khác trong tương lai. Để tương thích với các thiết bị trong tương lai, các bit này phải được ghi bằng logic 0 khi viết vào thanh ghi UBRRH.

Bit 11-0 là tốc độ truyền USART. Thanh ghi UBRRH có 4 bit trọng số lớn và UBRRL có 8 bit trọng số thấp của tốc độ truyền USART. Bộ phát và bộ thu tín hiệu nối tiếp sẽ bị hỏng nếu tốc độ truyền bị thay đổi trong lúc đang giao tiếp tín hiệu. Viết thanh ghi UBRRL sẽ kích hoạt cập nhật ngay lập tức tốc độ truyền.

Thanh ghi điều khiển và trạng thái USART có ba thanh ghi: UCSRA, UCSRB và UCSRC và các bit flag và bit điều khiển cho giao thức USART. UCSRA có các bit flag sau: RXC (USART Receive Complete), TXC (USART Transmit Complete), UDRE (USART Data Register Empty), FE (Frame Error), DOR (Data OverRun), PE (Parity Error), MPCM (Multi-processor Communication Mode) và bit điều khiển U2X (Double the USART Transmission Speed).

Thanh ghi UCSRB có các bit điều khiển sau: RXCIE (RX Complete Interrupt Enable), TXCIE (TX Complete Interrupt Enable), UDRIE (USART Data Register Empty Interrupt Enable), RXEN (Receiver Enable), TXEN (Transmitter Enable), UCSZ2 (Character Size), RXB8 (Receive Data Bit 8) và TXB8 (Transmit Data Bit 8). Thanh ghi UCSRC có các bit điều khiển sau: URSEL (Register Select), UPM1: 0 (Parity Mode), USBS (Stop Bit Select), UCSZ1: 0 (Character Size) và UCPOL (Clock Polarity).

Thanh ghi dữ liệu USART là bộ đệm các ký tự được gửi hoặc nhận qua cổng nối tiếp. Để bắt đầu gửi một ký tự, hãy ghi ký tự đó vào thanh ghi UDR. Sau đó, để kiểm tra một ký tự đã nhận, hãy đọc nó từ thanh ghi UDR.

Các chức năng chính của USART nối tiếp là khởi tạo cổng nối tiếp, gửi một ký tự, nhận một ký tự và gửi / nhận các chuỗi dữ liệu được định dạng.

Khởi tạo cổng nối tiếp bao gồm cài đặt tham số truyền thông USART (bit dữ liệu, bit stop và bit chẵn lẻ), kích hoạt bộ phát và bộ thu tín hiệu, cài đặt giao thức USART ở chế độ không đồng bộ và đặt tốc độ truyền.

Để gửi một ký tự, bit flag UDRE được đặt thành 1 và sau đó ghi ký tự vào thanh ghi UDR để truyền. Để nhận một ký tự bit flag RXC được đặt thành 1 và sau đó đọc ký tự nhận được từ thanh ghi UDR.

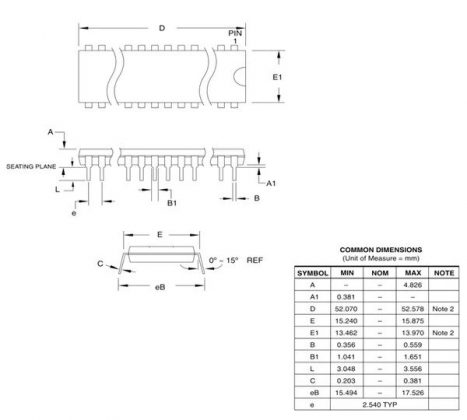

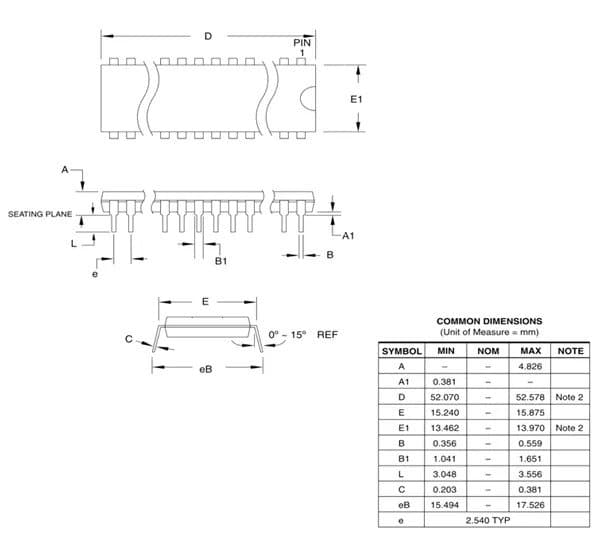

Đây là sơ đồ kích thước vật lý 2D cho packge DIP.

>>> 100+ Mã Sản Phẩm Dây Rút: https://mecsu.vn/san-pham/day-rut-nhua.5op

>>> 1000+ Mã Sản Phẩm Đầu Cosse: https://mecsu.vn/san-pham/dau-cosse.Q1j

>>> Mời anh em xem thêm