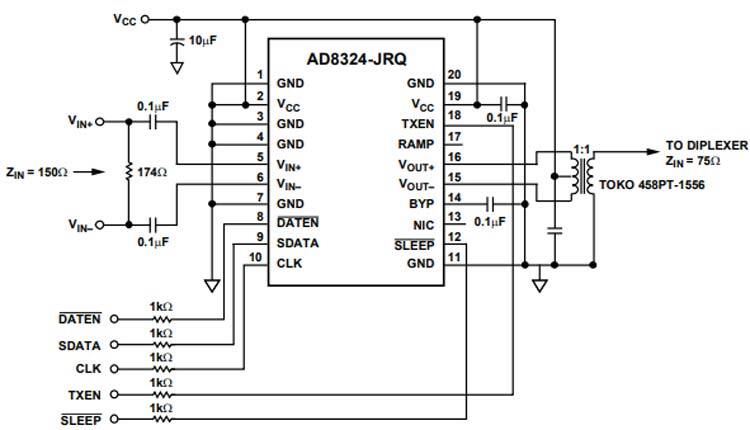

AD8324 là bộ khuếch đại chi phí thấp được thiết kế để điều khiển dây điện đồng trục. Các tính năng của AD8324 phù hợp nhất cho các ứng dụng DOCSIS 2.0 và EuroDOCSIS. Độ lợi của AD8324 được điều khiển digital có độ phân giải 8bit trong phạm vi 59dB, dẫn đến thay đổi độ lợi là 1 dB / LSB.

AD8324 nhận tín hiệu đầu vào vi sai hoặc đầu vào single-end. Đầu ra được chỉ định để điều khiển tải 75 Ω qua bộ biến áp 1: 1. Hiệu suất biến dạng –54 dBc đạt được với mức đầu ra lên đến 61 dBm ở băng thông 65 MHz.

Thiết bị này có chức năng chế độ nghỉ giúp giảm dòng điện tĩnh xuống 30 μA và chức năng tắt nguồn hoàn toàn giúp giảm dòng điện ngắt xuống 2,5 mA với điện áp cấp là 3,3V.

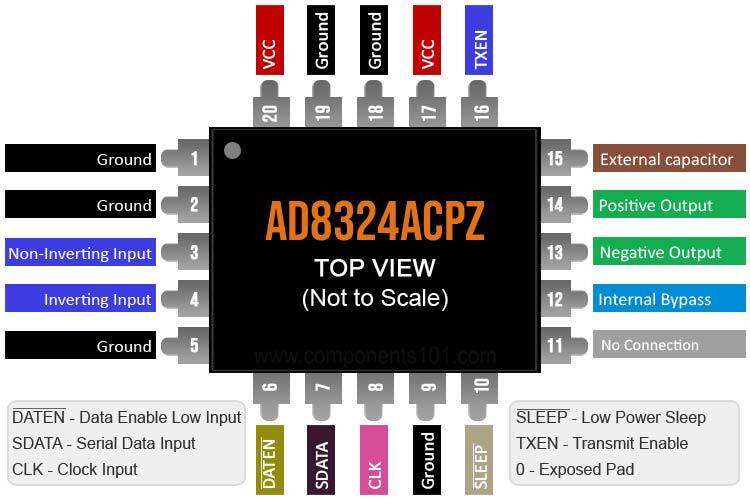

| Số chân | Tên chân | Mô tả |

| 1, 2, 5, 9, 18, 19 | Gnd | Chân nối đất bên ngoài chung |

| 3 | VIN + | Đầu vào không đảo, phân cực DC đến xấp xỉ VCC / 2. Phải được ghép nối với một tụ điện 0,1 μF xoay chiều |

| 4 | VIN– | Đầu vào đảo, phân cực DC đến xấp xỉ VCC / 2. Phải được ghép nối với một tụ điện 0,1 μF xoay chiều |

| 6 | Kích hoạt khi Đầu vào có logic thấp, Cổng này điều khiển chân dữ liệu song song 8bit và thanh ghi dịch. Quá trình chuyển đổi Logic 0 sang Logic 1 chuyển dữ liệu đã chốt tín hiệu (cập nhật mức tăng) và đồng thời ngăn việc truyền dữ liệu nối tiếp vào thanh ghi. Quá trình chuyển đổi Logic 1 sang Logic 0 ngăn chân dữ liệu (giữ chốt tín hiệu trước đó và đồng thời cho phép thanh ghi dịch truyền dữ liệu nối tiếp cho tải). | |

| 7 | SDATA | Đầu vào dữ liệu nối tiếp, Đầu vào digital này cho phép một word dữ liệu nối tiếp (độ lợi) 8bit được tải vào thanh ghi dịch bên trong với bit có trọng số lớn nhất (MSB) trước tiên. |

| 8 | CLK | Đầu vào xung clock, Cổng xung clock điều khiển tốc độ truyền dữ liệu của bộ truyề nối tiếp đến thanh ghi dịch chuyển Master-Slave 8-bit. Quá trình chuyển đổi Logic 0 sang Logic 1 chân bit dữ liệu và từ Logic 1 sang Logic 0 chuyển bit dữ liệu tới Slave. Điều này yêu cầu từ dữ liệu nối tiếp đầu vào phải hợp lệ sau hoặc trước khi xung clock chuyển đổi này. |

| 10 | Chế độ ngủ tiêu thụ nguồn điện thấp, Ở chế độ ngủ, dòng điện cung cấp của AD8324 giảm xuống còn 30 μA. Logic 0 tắt nguồn thiết bị (trạng thái ZOUT cao) và Logic 1 bật nguồn thiết bị. | |

| 11 | NIC | Không kết nối với chân này |

| 12 | BYP | Chân bypass bên trong, chân này phải được tách ra bên ngoài (tụ điện 0,1 μF). |

| 13 | VOUT- | Tín hiệu đầu ra âm, phải được phân cực thành VCC. |

| 14 | VOUT + | Tín hiệu đầu ra dương, phải được phân biệt với VCC |

| 15 | RAMP | Tụ RAMP bên ngoài (Tùy chọn) |

| 16 | TXEN | Kích hoạt truyền dữ liệu, Logic 0 tắt truyền và Logic 1 cho phép truyền |

| 17,20 | VCC | Điện áp nguồn cấp dương bên ngoài chung. |

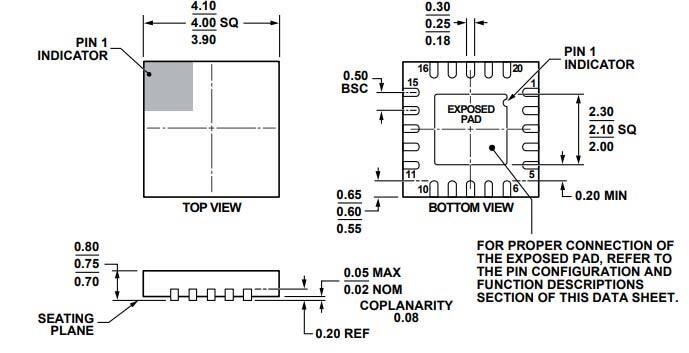

| 0 | EPAD | Tấm tiếp xúc, Tấm tiếp xúc phải được kết nối với một mặt phẳng đồng đặc có khả năng chịu nhiệt thấp. Điều này chỉ áp dụng cho package LFCSP 20 chân. |

DS8921, MT3608 , DRV632, DRV135, AM26LS33

AD8324 chủ yếu được thiết kế để sử dụng như bộ khuếch đại công suất ngược dòng (PA) trong các modem cáp được chứng nhận về Data-Over-Cable Service Interface Specification (DOCSIS) và hộp giải mã CATV.

Tín hiệu ngược dòng là tín hiệu quadrature phase-shift keying (QPSK) hoặc tín hiệu quadrature amplitude modulation (QAM) được tạo ra bởi bộ xử lý tín hiệu digital (DSP), bộ điều chế QPSK / QAM chuyên dụng hoặc bộ chuyển đổi digital sang analog (DAC).

Trong mọi trường hợp, tín hiệu phải được lọc lowpass trước khi đưa vào PA để lọc nhiễu ngoài dải và sóng hài bậc cao khỏi tín hiệu được khuếch đại.

Do khoảng cách khác nhau giữa modem cáp và đầu nối, PA ngược dòng phải có khả năng thay đổi công suất đầu ra bằng cách cấp độ lợi hoặc độ suy giảm tín hiệu. Khả năng thay đổi công suất đầu ra của AD8324 đảm bảo rằng tín hiệu từ modem cáp có mức phù hợp khi đến đầu nối.

Đường dẫn tín hiệu ngược dòng thường bao gồm bộ tách kênh và bộ tách cáp. AD8324 được thiết kế để khắc phục tổn thất liên quan đến các thành phần thụ động này trong đường cáp ngược dòng.

AD8324 bao gồm ba chức năng analog trong chế độ cho phép truyền. Bộ khuếch đại đầu vào (tiền khuếch đại) có thể được sử dụng trong cấu hình single-end hoặc độc lập. Nếu đầu vào được sử dụng trong cấu hình vi phân, hãy đảm bảo rằng tín hiệu đầu vào lệch pha 180 ° và có biên độ bằng nhau.

Một vernier được sử dụng trong giai đoạn xử lý đầu vào để điều khiển các bước tăng 1 dB nhỏ. Giai đoạn xử lý này điều khiển một bộ DAC cấp phần lớn chuyển đổi tín hịe cho AD8324.

Các tín hiệu trong khối preamp và DAC được phân biệt để cải thiện tỷ lệ khử nguồn cấp điện (PSRR) và độ tuyến tính. Một dòng điện vi sai được đưa từ DAC vào giai đoạn xử lý đầu ra. Giai đoạn đầu ra duy trì trở kháng đầu ra vi sai 75 Ω ở tất cả các chế độ công suất.

>> Mời anh em xem thêm